Pojawienie się chipletów • Artykuły • Zestaw wiedzy, zestawy projektowania chipletów dla heterogenicznej integracji 3D IC | Oprogramowanie Siemens

Korzystanie z zestawów projektowych chipletów, aby utorować drogę dla heterogenicznej integracji IC 3D

Contents

- 1 Korzystanie z zestawów projektowych chipletów, aby utorować drogę dla heterogenicznej integracji IC 3D

- 1.1 Pojawienie się chipletów

- 1.2 Preambuła

- 1.3 Chiplet, Quésaco ?

- 1.4 Ekonomiczne aspekty chipletów

- 1.5 Dwa przykłady: AMD i Intel (Altera)

- 1.6 Korzystanie z zestawów projektowych chipletów, aby utorować drogę dla heterogenicznej integracji IC 3D

- 1.7 Budowanie ekosystemu dla udanego 2.Integracja modelu chipletów 5D i 3D

- 1.8 Budowanie ekosystemu dla udanego 2.Integracja modelu chipletów 5D i 3D

- 1.9 Wyciekły obraz ujawnia ambitny projekt chipleta dla GPU AMD Radeon

- 1.10 Wyciekły obraz ujawnia ambitny projekt chipleta dla GPU AMD Radeon

Kilka lat później pierwsi procesory pojawiły się w szczególności Intel 4004, dziś stosunkowo proste. Wtedy procesory stały się bardziej złożone.

Pojawienie się chipletów

Po dyskusji w JZDS i na niezgodę, powiedziałem sobie, że napisanie artykułu na temat chipletów będzie korzystne dla największej liczby. I zachowałby pisemny utwór sprzeczny z tym, co może się stać z JZDS

Zamiast pisać bardzo długi bilet, wolę format artykułu, aby uzyskać trochę więcej w szczegółach. Mam nadzieję, że będę w stanie nauczyć cię, czym są chiplety, dlaczego ta technologia została stworzona i dlaczego rozwinę się w nadchodzących latach.

- Preambuła

- Chiplet, Quésaco ?

- Ekonomiczne aspekty chipletów

- Dwa przykłady: AMD i Intel (Altera)

Preambuła

W tym artykule opowiada o koncepcjach komputerowych, elektronicznych i architektury komputerów, które można wystarczająco zaawansować dla niektórych czytelników. Oferuję ci trochę popularyzacji w tej preambule, aby zrozumieć trochę lepiej, o czym mówimy.

W przypadku purystów zostaną skróty, ta popularyzacja może być w stanie zawierać dobrowolnie nieprecyzyjne informacje, aby ułatwić zrozumienie.

Chiplet, Quésaco ?

Zacznijmy od najtrudniejszych, określ, czym jest chiplet !

Rzeczywiście termin chiplet pojawił się w latach siedemdziesiątych, ale jego użycie wystartowało głównie w ostatnich latach, dla tych, którzy są zainteresowani złożonymi procesorami lub układami elektronicznymi, takimi jak FPGA (układy, których wewnętrzne drzwi logiczne można przeprogramować). Dla innych, na dole pokoju, być może nigdy nie słyszałeś o tym terminie, naprawimy to !

Wróćmy do podstaw tego, czym jest układ elektroniczny: kawałek grawerowanego krzemu (słynne tranzystory), który jest zamknięty w przypadku. Z komponentami skrzyżowania małe złote lub srebrne nici łączą nogi komponentu z kawałkiem krzem. Na początku układy składają się z tranzystorów wygrawerowanych z dość gruboziarnymi rozdzielczościami (w porównaniu z dziś), a funkcje były dość podstawowe: logiczne drzwi, wzmacniacze operacyjne itp. Był to jednak już ogromny postęp pod względem miniaturyzacji !

W tym czasie komponenty miały nogi krzyżowe i konieczne jest podłączenie krzemowego chipu z tymi nogami. Jest wykonany z cienkich synów srebra lub złota, które są przyspawane między układem a nogami w obudowie.

Kilka lat później pierwsi procesory pojawiły się w szczególności Intel 4004, dziś stosunkowo proste. Wtedy procesory stały się bardziej złożone.

Z lat 70. IBM opracował komponenty MCM (Multi-Chodu) w tym kilka wiórów krzemowych w jednym przypadku. Ale ta technologia rozwinie się głównie pod koniec lat 90. Możemy zwrócić uwagę na Pentium Pro z Intela wydanego w 1995 roku. Procesor ten obejmował dwa krzemowe układy: jeden dla procesora ściśle mówiąc, a drugi dla pamięci pamięci podręcznej L2 (pamięć buforowa między procesorem a pamięcią RAM, znacznie szybciej, ale znacznie droższy, ponieważ wygrawerowany z procesorem).

Jak widać na zdjęciu, dwa układy mają mniej więcej ten sam rozmiar, a Intel oferował kilka rozmiarów pamięci podręcznej L2. Zaletą oddzielania procesora pamięci pamięci podręcznej było możliwość zapisania skali na układie procesora, oferując różne rozmiary pamięci pamięci podręcznej poprzez umieszczenie w przypadku innego układu rozmiaru.

Ten typ komponentu pozostaje stosunkowo słabo rozwinięty, nawet jeśli IBM nadal rozwijał komponenty MCM. Zwróć uwagę na Power5 IBM wydanego w 2004 roku, w którym cztery procesory wprost za pomocą układu pamięci Cache L3. Współpliżenie pcheł odbywa się w obudowie.

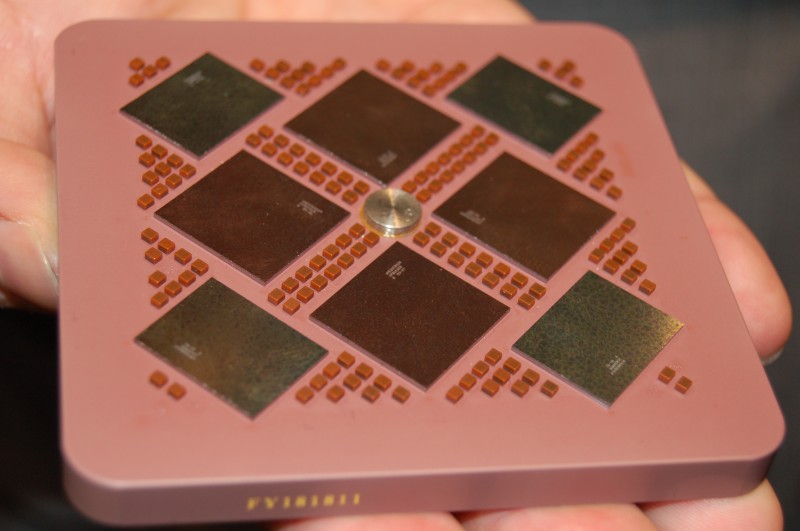

Dziś technologia ewoluowała, a układy MCM są obecne w produktach konsumenckich z procesorami AMD. Tutaj możemy zobaczyć procesor EPYC 7702 (wydany w sierpniu 2019 r.) Złożony z 9 połączonych wiórów krzemowych: 8 układów zawierających rdzenie i pamięć pamięci podręcznej oraz środkowy układ łączący drugą 8 i który zarządza DDR, a także wejście do sygnałów/ wyjście (SATA, PCI Express, USB itp.)).

Ale powiedz mi Jamy, co to jest chiplet ?

Ach tak, trochę czerpałem

W rzeczywistości chiplet jest jednym z krzemowych układów obecnych w MCM. Chiplet ma być powiązana z innymi chipletami. Tak, to jest stosunkowo proste, ale musiałeś pokazać kilka fajnych zdjęć do zrozumienia

Niemniej jednak, aby być nieco bardziej precyzyjnym na temat znaczenia chipletów, niekoniecznie jest połączenie kilku różnych układów. Istnieje również pojęcie ogólnego układu, które można ponownie wykorzystywać i nie poświęcić określonemu odniesieniu do procesora.

Ekonomiczne aspekty chipletów

Po tym wprowadzeniu podczas obrazu, zrozummy teraz, dlaczego chiplety będą się rozwijać w przyszłości. Aby to zrobić, konieczne jest powrót do procesu produkcji pcheł elektronicznych.

Usiądź wygodnie w fotelu, ponieważ podróż z piaszczystej plaży będzie długa

Nie, czekaj !

Spędzimy całą część produkcji krzemu. To nas zainteresuje rozkład pchłów (umierać) na krzemowym ciasto (opłatek), a w szczególności ewolucja wydajności wraz ze wzrostem grawerowania finezji.

Ale przed tym aspektem wydajności musimy porozmawiać o maksymalnej fizycznej wielkości matrycy. Rzeczywiście, na krzemie naleśnik ten sam konstrukcja chipu powtarza się kilka razy (dziesiątki, a nawet sto razy). Wrażenie tego projektu odbywa się optycznie za pomocą światła ultrafioletowego. Istnieje jednak cały zestaw soczewek i mechanizmów optyczny.

Im bardziej komplikujemy pchły, tym bardziej chcemy umieścić tranzystory, więc musimy albo zwiększyć rozmiar układu, albo zwiększyć delikatność grawerowania, aby pasować do większej liczby tranzystorów na tej samej powierzchni. Ale odczuwa się też inne ograniczenia i ograniczenia.

Właśnie dlatego zasada chipleta jest interesująca, aby ominąć te granice: użyj kilku małych układów krzemionowych połączonych ze sobą, aby stworzyć bardziej złożony chip, ale niemożliwy do wygrawerowania w sposób monolityczny.

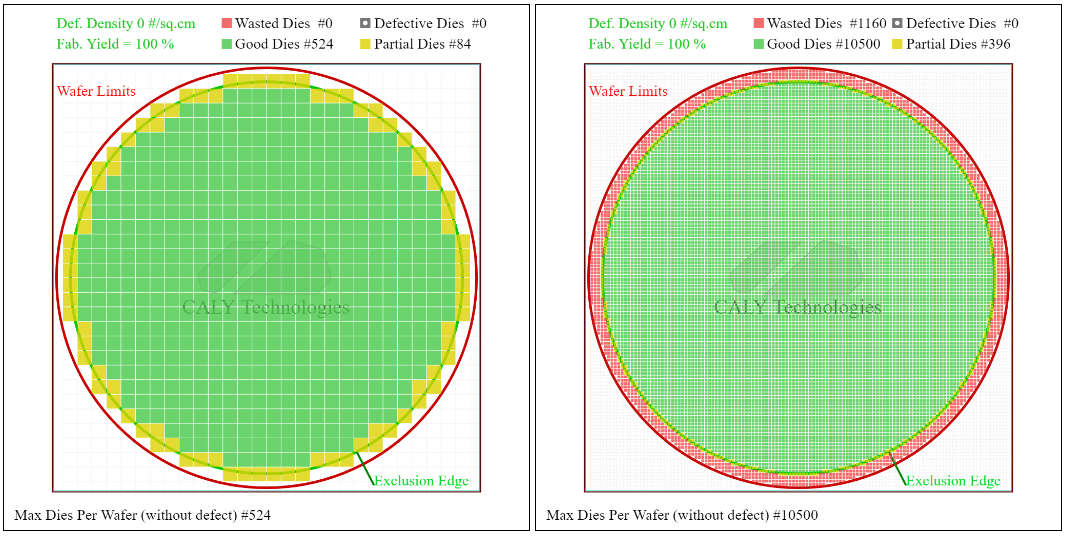

Teraz wróć do wydajności (dawać po angielsku). Najpierw wafle mają kształt okrągłego i chcemy go wygrawerować z prostokątnymi frytkami. Cały krzem nie jest używany. Ale im mniejsze umiera na krawędziach i tym bardziej możemy mieć całe umieranie. Jest to ta sama zasada, co aliasing w grze wideo: im więcej pikseli używane do tworzenia okrągłego kształtu są małe, a im mniej zdajemy sobie sprawę.

W powyższym przykładzie, jeśli zgłosimy, że częściowe umiera na całkowitą liczbę matryc (dobre i stronniczość), uzyskujemy stosunek 13.8 % w przypadku matryc 5 × 5 mm i 3.6 % w przypadku 1 × 1 mm umiera. Im mniejsza matryca, tym bardziej ważne mogą mieć na krawędziach, co zwiększa wydajność.

Możesz także zrobić dużą mieszankę matrycy na środku opłatek i użyć mniejszych matryc na krawędziach, aby zoptymalizować wydajność z powodu aliasingu.

Powiedz Jamy, dlaczego używamy okrągłych płytek do robienia prostokątnych pcheł ?

Cóż, dzieje się tak ze względu na metodę wytwarzania silikonu zwanego procesem cZochralski, który daje krzem w postaci cylindrów, pokrojonych na bardzo drobne plastry Wafle.

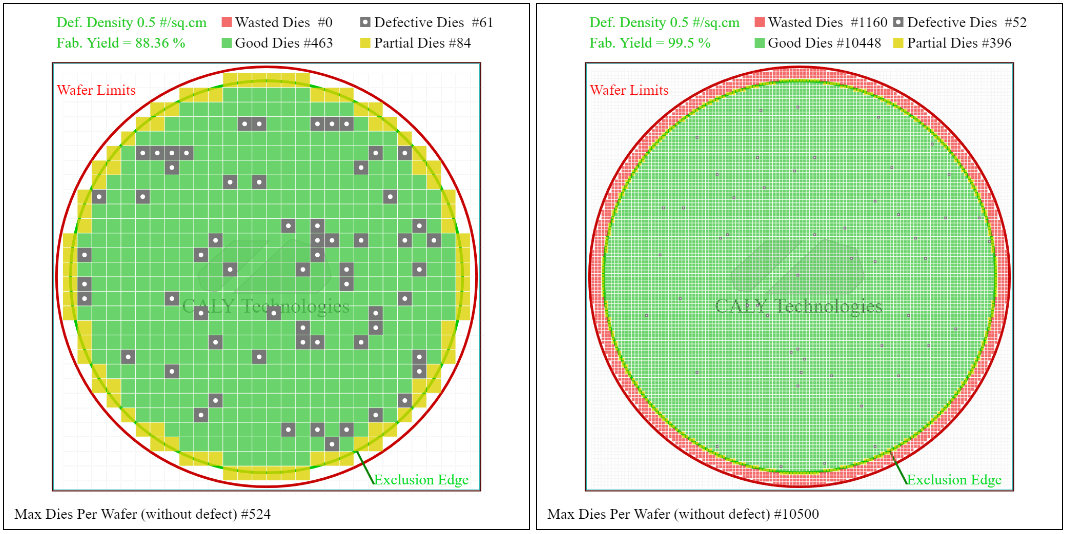

Po drugie, na wydajność wpływają wady, które mogą pojawić się na waflu. Możesz pomyśleć o ziarnach pyłu, które spadają na wafel.

Wznowiłem poprzedni przykład, dodając gęstość błędu 0.5 na cm². Teraz porównaj Produkcja plonów co odpowiada stosunku między liczbą matryc funkcjonalnych a całkowitą liczbą wytwarzanych produktów. W przypadku matrycy 5 × 5 mm wydajność wynosi 88.4 %, podczas gdy umiera 1 × 1 mm, wydajność wynosi 99.5 %.

Dlatego podwójnie interesujące jest posiadanie małych matryc do optymalizacji produkcji pcheł elektronicznych. Niemniej jednak cięcie złożonego układu na kilka mniejszych układów wymaga przekazania tych różnych układów między nimi, dlatego musimy dodać elementy komunikacyjne, które zajmują dodatkową przestrzeń i wykorzystać dodatkową energię.

Ponadto użycie chipletów może umożliwić użycie matryc różnej finezji grawerowania zgodnie z funkcjami umożliwiającymi modulowanie kosztów końcowego układu z wydajnością.

Wreszcie, kolejnym ekonomicznym aspektem jest złożoność rozwijania nowych funkcji. To zwykle ma wyspecjalizowane firmy (lub przynajmniej start-upy na początku) oferujące bloki własności intelektualnej (funkcji) gotowe do użycia. Na przykład producent procesorów będzie mógł skupić się na rozwoju samego procesora podczas kupowania matryc dla funkcji takich jak PCI Express, USB lub DDR.

Aby ułatwić interoperacyjność chipletów pochodzących od różnych producentów, głównych graczy, takich jak Intel, AMD, ARM, Qualcomm, Samsung lub TSMC, stworzyli standard komunikacji między chippletami, UCIE (Universal Chiplet Interconnect Express)).

Dwa przykłady: AMD i Intel (Altera)

AMD EPYC

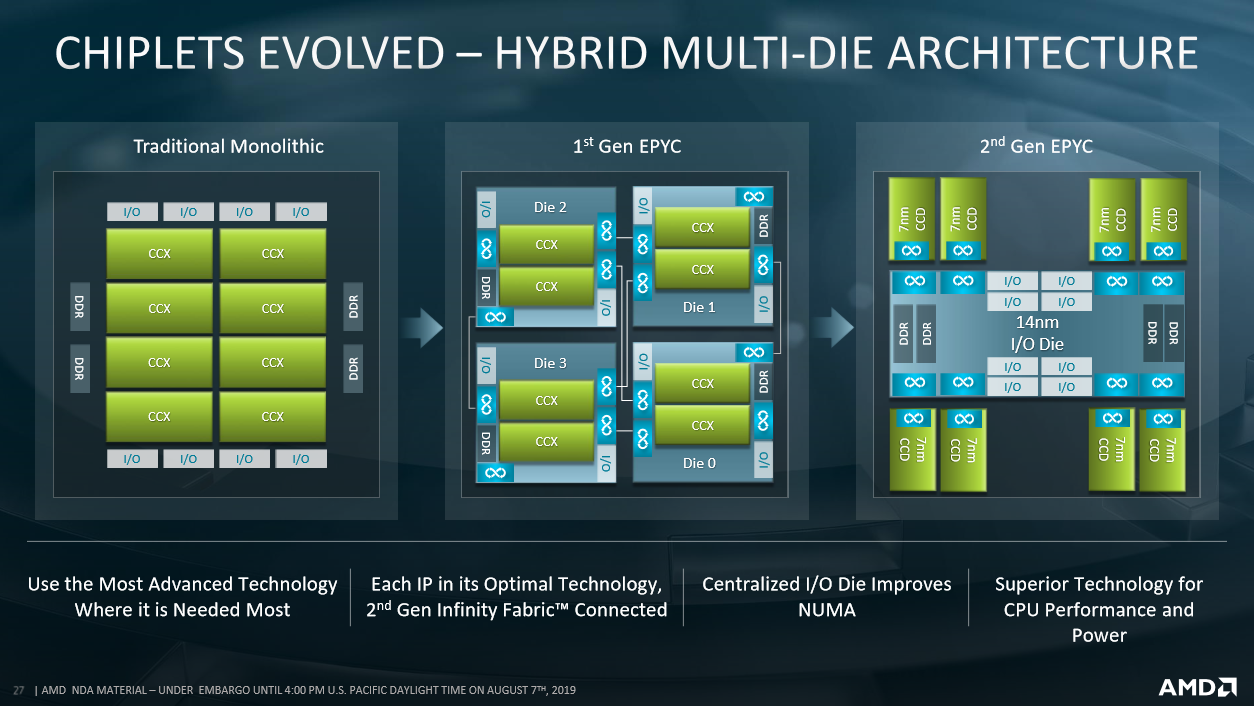

Dzisiaj coraz więcej procesorów korzysta z tej techniki chipletów. AMD używa chipletów od pierwszej generacji procesorów EPYC, w których różne serca są połączone przezTkanina nieskończoności.

Pierwsza generacja procesorów EPYC widziała zestaw matryc, które można utożsamiać z kompletnymi procesorami połączonymi przezTkanina nieskończoności Aby utworzyć ostateczny procesor. Chiplety były zatem rodzajem małego autonomicznego procesora: każda matryca zarządzała jego wpisami/wyjściami i miał swój kontroler DDR.

Te umierania, a raczej chiplety, mają dwa Kompleks obliczeniowy rdzenia (CCX, zestaw czterech rdzeni z pamięcią pamięci podręcznej), a także kontroler DDR, zarządza wejściami/wyjściami (na przykład PCI Express) i ma moduły komunikacyjne dlaTkanina nieskończoności.

Mała subtelność, zawsze są cztery chiplety na EPYC pierwszej generacji. Aby zmieniać liczbę serc, AMD dezaktywuje serca w CCX. Na przykład, aby mieć 24 rdzenie, CCX ma tylko 3 aktywne rdzenie

W związku z tym pierwsza generacja wykorzystała zasadę chipletów jako rodzaj kopii/przyklejonej matryc zamiast opracowywania dużej matrycy monolitycznej.

Dla drugiej generacji AMD nieco dalej popycha tę koncepcję. Rzeczywiście, CCX są teraz niezależne, pogrupowane w parach w obrębie Rdzeń obliczeniowy (CCD) połączone przez Tkanina nieskończoności do matrycy zarządzającej DDR i zgłoszeniami/wyjściami I/O Die (Iod).

AMD w pełni wykorzystuje to zwiększone oddzielenie od funkcji. Rzeczywiście CCD jest grawerowane w 7 nm, podczas gdy IOD jest wygrawerowany w 14 nm.

Poniżej prezentacji AMD podsumowującej fragment w chipletach procesorów EPYC.

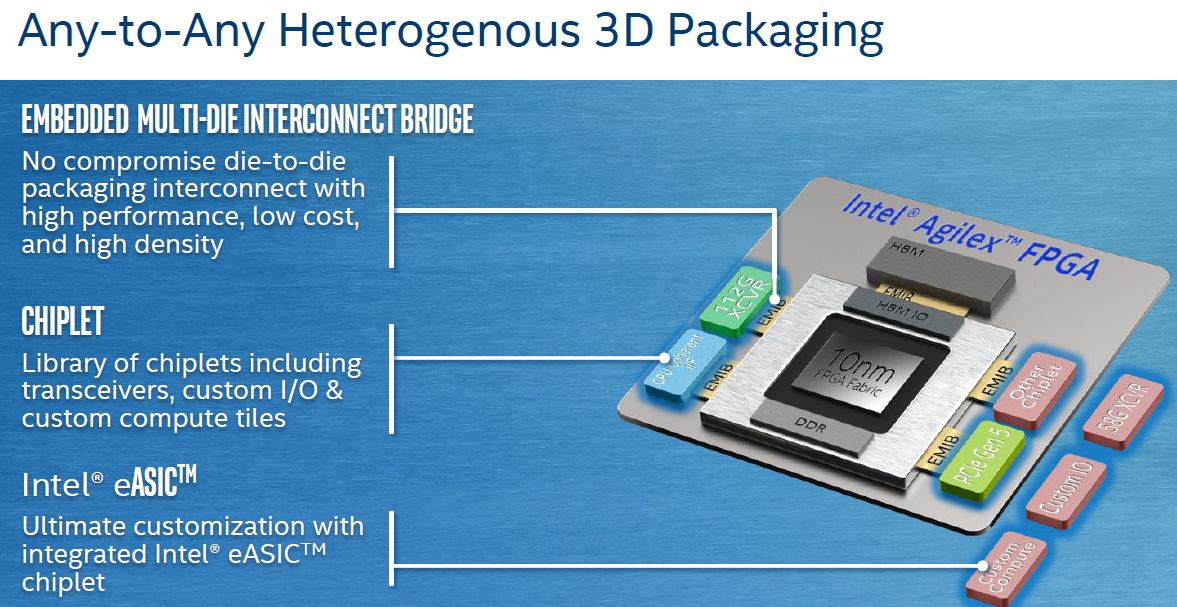

Intel FPGA (altera)

Procesory Intel są zawsze monolitycznymi układami, z wyjątkiem kilku wyjątków, jak mogliśmy zobaczyć na początku tego artykułu. Niemniej jednak w sektorze Intel FPGA (rekonfigurowalne FPGA) wykorzystuje chiplety dla najnowszej generacji, Agilex.

Te chiplety dotyczą głównie rodzaju zastosowanego transcense (szybkie linki) i są nazywane Płytki. Jeśli Intel oferuje predefiniowane zakresy od tych płytek, musi być możliwe, aby dostosować wióry własne.

Płytki są podzielone przez maksymalną prędkość nadajników i obsługiwane protokoły (Ethernet, PCI Express itp.): 16G dla p, 28 g dla h, 32 g dla r itp.

Intel przywołuje również w przyszłości możliwość połączenia niestandardowych chipletów, które zapewniłyby dodatkowe funkcje. Obecnie firmy wydały chiplet ADC/DAC (Jariett Technologies), a także kolejne połączenie optyczne (Ayar Labs).

Wreszcie nie możemy nie wierzyć, że żetony monolityczny są martwi. Zawsze mają zalety, szczególnie pod względem komunikacji wewnętrznej i opóźnień, co może być kluczowe dla niektórych aplikacji wymagających dużych układów.

Tak jest w przypadku Broadcom i jego wiórów Switch 400G, których wybór wyjaśnia projektant w tym filmie: https: // www.youtube.Com/Watch?V = B-Cogmbaug4

Mam nadzieję, że ten artykuł ma dla ciebie więcej i pozwolił ci dowiedzieć się więcej o produkcji obecnych żetonów. Próbowałem popularyzować złożony temat, mam również nadzieję, że udało mi się zatrzymać po pierwszym akapicie

Nie wahaj się zostawić komentarz, jeśli niektóre punkty pozostaną dla ciebie tajemnicze, postaram się podać szczegóły.

6 komentarzy

Ta odpowiedź była przydatna

Doskonały artykuł, dziękuję @ Zeql !

„Rzuć mnie na wilki, a zwrócę paczkę.” – Seneca

Ta odpowiedź była przydatna

Zastanawiałem się, jak bardzo pojawienie się Chipletów było w stanie rozważyć pewną ewolucję w sprzęcie ( Konsumenci To Klasa serwera) W przyszłości, a nawet zmiana paradygmatu w drodze, aby zaprojektować wysoce i optymalne maszyny.

Niektóre dobrze zintegrowane systemy (szczególnie w Apple) nie są oparte wyłącznie na bardzo wydajnym „klasycznym” procesorze, ale także na kilku specjalistycznych układach pomocniczych, które rozładowują ogólne procesory. W ograniczonym systemie jako smartfon możemy znaleźć układy transkodowania H265, jednostki obliczeniowe dla AI (Silnik neuronowy Apple) i oczywiście klasyczna jednostka graficzna.

Dlatego podejmuję schemat AMD EPYC z drugiej generacji i zastanawiam się, czy chiplety byłyby prostym sposobem na produkcję komercyjnie i przemysłowo opłacalną z kompletnych jednostek, które wyruszają kilka wyspecjalizowanych układów, aby osiągnąć optymalną wydajność w niektórych zadaniach. Na przykład jednostka może zapewnić klasyczne CCD, ale także DSP, GPU, Transco H265/AV1/VP9/…, chip do wykonania AE itp. i podłącz to poprzez produkcję IOD/Infinity. Każdy producent maszyn/serwerów może zatem skomponować swoją gotową do użycia jednostkę końcową, skomponując się i bez kosztów uprzemysłowienia R&D/.

Przypomina mi koncepcję APU, ale nie wiem, czy istnieje raport.

Ta odpowiedź była przydatna

Zastanawiałem się, jak bardzo pojawienie się Chipletów było w stanie rozważyć pewną ewolucję w sprzęcie ( Konsumenci To Klasa serwera) W przyszłości, a nawet zmiana paradygmatu w drodze, aby zaprojektować wysoce i optymalne maszyny.

Niektóre dobrze zintegrowane systemy (szczególnie w Apple) nie są oparte wyłącznie na bardzo wydajnym „klasycznym” procesorze, ale także na kilku specjalistycznych układach pomocniczych, które rozładowują ogólne procesory. W ograniczonym systemie jako smartfon możemy znaleźć układy transkodowania H265, jednostki obliczeniowe dla AI (Silnik neuronowy Apple) i oczywiście klasyczna jednostka graficzna.

Dlatego podejmuję schemat AMD EPYC z drugiej generacji i zastanawiam się, czy chiplety byłyby prostym sposobem na produkcję komercyjnie i przemysłowo opłacalną z kompletnych jednostek, które wyruszają kilka wyspecjalizowanych układów, aby osiągnąć optymalną wydajność w niektórych zadaniach. Na przykład jednostka może zapewnić klasyczne CCD, ale także DSP, GPU, Transco H265/AV1/VP9/…, chip do wykonania AE itp. i podłącz to poprzez produkcję IOD/Infinity. Każdy producent maszyn/serwerów może zatem skomponować swoją gotową do użycia jednostkę końcową, skomponując się i bez kosztów uprzemysłowienia R&D/.

Przypomina mi koncepcję APU, ale nie wiem, czy istnieje raport.

Powinieneś więc wiedzieć, że chip jest często wykonywany z IP (własność intelektualna): funkcja sprzedawana jest dość gotowa na poziomie „tranzystorów”, ale należy ją zintegrować z jego projektem.

Klasycznym przykładem jest kontroler DDR3 w MicroController na tablicy. Producent mikrokontrolera niekoniecznie opanuje DDR3 i nie ma umiejętności, czasu (ani pragnienia) utworzenia kontrolera DDR3. Dlatego kupuje IP od kontrolera i integruje go z jego projektem.

Musisz uda się zobaczyć różnicę między możliwością adresu IP i chipletu. Dla mnie chiplet ma nadejść i przynieść jedną lub więcej zaawansowanych funkcji i które już przeszły testy grawerowania, a zatem dodatkowy krok w projekcie. Ale pozostaje problem testowania pełnej gleby ze wszystkimi chiplami. Nie możemy więc stworzyć setek wariantów, takich jak Lego. Wymaga minimum rzeczywistości ekonomicznej.

Ale tak, dla określonego tomu możemy stworzyć gniazda à la carte.

Dużą zaletą jest po stronie produkcyjnej układu: jeśli IP może zostać odrzucone dla innej finezji grawerowania, chip na korzyść, że można zawsze wygrawerować w początkowej finezie (jeśli jest wystarczająca), gdy inne części mogą być ulepszonym dzięki mniejszemu grawerowaniu.

Ta odpowiedź była przydatna

Poza tym myślałem, że chiplety mogą być używane w modułowej konstrukcji. Przyjmujesz projekt z 4 układami, pchły z błędami są dystrybuowane w całej produkcji, a te z 3 wiórami, które działają na 4, będą w zasięgu poniżej i nieco tańsze niż te z 4, które pracują.

Co upraszcza projektowanie i uprzemysłowienie w odniesieniu do konwencjonalnej działalności.

Miłośnik bezpłatnego oprogramowania i dystrybucji GNU/Linux Fedora. #Jessuisarius

Ta odpowiedź była przydatna

Dziękuję za ten ciekawy mega artykuł. Kochałbym cię za dużo czasu, aby szczegółowo opisać każdy punkt, którego nie wyjaśniasz w samouczku, aby naprawdę zrozumieć rzeczy, ale i tak interesujące .

Korzystanie z zestawów projektowych chipletów, aby utorować drogę dla heterogenicznej integracji IC 3D

Chiplet to matryca ASIC specjalnie zaprojektowana i zoptymalizowana pod kątem pracy w pakiecie w połączeniu z innymi chipletami. Heterogeniczne zintegrowane (HI) obejmuje liczbę wielokrotnych matryc lub chipletów na chiplety systemowe (SIP). Urządzenia te oferowane jako konsekwentne korzyści, obejmują wydajność, moc, obszar, koszt i TTM.

Chiplet Design Exchange (CDX) składa się z dostawców EDA, chiplet

Dostawcy/asemblery i integratorzy SIP i jest otwartą grupą roboczą, która zaleca znormalizowane modele i przepływy pracy w celu ułatwienia ekosystemu chipletów. To seminarium internetowe podsumowuje oferty projektowe chipletów (CDK), aby pomóc standaryzować 2.5d i 3.Projekty IC, aby stworzyć otwarty ekosystem.

Budowanie ekosystemu dla udanego 2.Integracja modelu chipletów 5D i 3D

Podobnie do procesu SOC, potrzebujesz ekosystemu do chippletów. Klucz umożliwia ogólne przyjęcie rynku i wdrożenie projektów opartych na chipletach obejmowało:

- Technologia: 2.5 d interpozycja i procesy wytwarzania i montażu w stosach 3D

- IP: znormalizowane modele chipletów

- Przepływy pracy: przepływy EDA i przepływy PDK, CDK, DRM i reguły montażu

- Modele biznesowe: Chiplet Marketplace

Początkowe skupienie CDX to 2.Modele chipletów oparte na oparciu o 5D z 3D do naśladowania. Dowiedz się więcej o tych wysiłkach w seminarium internetowym.

Wymiana Design Chiplet (CDX) składa się z dostawców EDA, dostawców/asemblerów chipletów i integratorów SIP oraz jest otwartą grupą roboczą, która zaleca znormalizowane modele i przepływy pracy, aby ułatwić ekosystem chipletów. To seminarium internetowe podsumowuje oferty projektowe chipletów (CDK), aby pomóc standaryzować 2.5d i 3.Projekty IC, aby stworzyć otwarty ekosystem.

Budowanie ekosystemu dla udanego 2.Integracja modelu chipletów 5D i 3D

Podobnie do procesu SOC, potrzebujesz ekosystemu do chippletów. Klucz umożliwia ogólne przyjęcie rynku i wdrożenie projektów opartych na chipletach obejmowało:

- Technologia: 2.5 d interpozycja i procesy wytwarzania i montażu w stosach 3D

- IP: znormalizowane modele chipletów

- Przepływy pracy: przepływy EDA i przepływy PDK, CDK, DRM i reguły montażu

- Modele biznesowe: Chiplet Marketplace

Początkowe skupienie CDX to 2.Modele chipletów oparte na oparciu o 5D z 3D do naśladowania. Dowiedz się więcej o tych wysiłkach w seminarium internetowym.

Wyciekły obraz ujawnia ambitny projekt chipleta dla GPU AMD Radeon

Wyciekły obraz ujawnia ambitny projekt chipleta dla GPU AMD Radeon

- przez

- W wiadomościach

- 16 sierpnia 2023

Wyciekany obraz pojawił się, ujawniając projekt GPU z Chipletami Radeon, podobno z anulowanego projektu Chip 4C Navi 4C. Projekt obecny od 13 do 20 różnych chipletów na jednym procesorze GPU, zeznając na ambitne podejście AMD. Ta bardziej złożona konstrukcja chipletów różni się od krzemu Navi 31 używanego obecnie w Radeon Rx 7900 XTX. Podczas gdy poprzednia iteracja GPU została uznana za pierwszą generację, nie zastosowała prawdziwego projektu chipletów, takiej jak ostatnie procesory Ryzen AMD. Jednak koncepcja ujawnienia Navi 4C stanowi znaczący postęp, ponieważ zawiera kilka chipletów obliczeniowych, a także odrębne chiplety we/wy, na jednym podłożu. Wyciekły obraz przedstawia 13 chipletów, z możliwością dodatkowych układów kontrolera pamięci, które nie są wyświetlane na obrazie.

Aby potwierdzić autentyczność obrazu, podkreślono odpowiedni patent z 2021 r. Wzory patentowe bardzo przypominają projekt pokazany na wyciekając.

Niestety, projekt GPU przedstawiony na wyciekającym obrazie został anulowany. Zgadza się to z ostatnimi relacjami sugerującymi, że akcent AMD dla następnej generacji GPU będzie na modnych układach monolitycznych Navi 43 i Navi 44 przez. Spekuluje się jednak, że AMD przekierowuje swoje wysiłki na rozwój GPU złożonego z kilku chipletów obliczeniowych dla segmentu wysokiego poziomu przyszłego zakresu kart graficznych, potencjalnie z RDNA 5.

Chociaż realizacja kilku chipletów obliczeniowych dla grafiki gry jest bardziej złożona niż w przypadku tradycyjnych obliczeń procesora, decyzja AMD o pokonaniu przeszkód projektowych i praca nad lepszym rozwiązaniem dla rDNA 5 jest postrzegana jako pozytywny krok. Byłoby korzystne, aby AMD miał plan ratunkowy, taki jak nowy węzeł dla ulepszonej wersji Navi 31.